Microinstructions Done

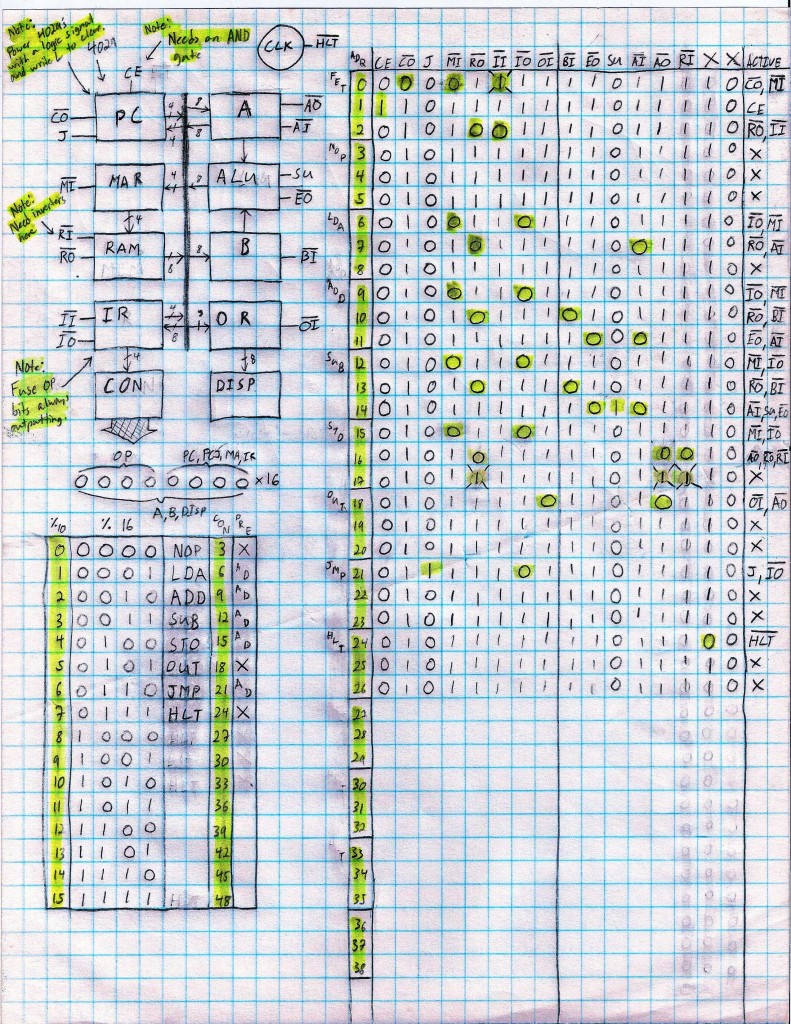

I finished the microinstructions for the control matrix of my computer. The block diagram on the upper left is the architecture of the computer itself. The chart below it is a list of OP codes for different macroinstructions. The chart on the right is the list of each individual microinstruction that makes up each macroinstruction.

For sake of simplicity I’ve also put all of this data into an excel worksheet that reads out base-10 numbers to make programming the NVRAM easy if I choose to use my Arduino for a programmer.

24 Responses to Microinstructions Done

Leave a Reply Cancel reply

Recent Comments

Archives

Language

Have you considered using an FPGA? The advantage there is you don’t need to spend money on chips, effort on wiring everything up, you have huge amounts of gates to work with and most importantly you can easily change the design as simply as changing a few lines of code without having to rewire your hardware.

To top it all off, in your FPGA design environment you have access to hardware a simulator, think of it as a free multichannel logic analyser that will prove invaluable in troubleshooting.

I imagine FPGAs can seem scary at first but speaking from personal experience, once you’ve gone there you’d never go back to discrete logic chips.

Many people tried to convince me to use a FPGA when I started off with this project. I decided that it would not be nearly as fun or a challenge. I am not saying that I do not like them. In fact, I would love to have one to experiment with. Using discreet logic with actual IC’s is a lot more appealing to me, however, with this project. This way I can get a true understanding of how much work goes into the design and operation of a CPU.

For instance, with an FPGA I would have not learned the imperative knowledge of TTL and CMOS voltage differences or gained the breadboard skills that I now have. And with a breadboard I have something truly physical to show for my work.

I am into software as well so FPGA’s are implicitly intriguing to me. I might buy one in the future (perhaps after this project), but until then I’m perfectly content with throwing out my back to place breadboard wires.

You may want to consider writing a microcode assembler. You could probably create something workable in two or three pages of Python. In my own experience creating a computer from scratch, it was a huge time saver.

Just wanted to pass along some docs on an 8bit CPU that was designed by one of the professors at the University of Florida incase you need some well-documented reference material.

Keep up the good work! It looks great and you will definitely learn a lot.

HTML didn’t pull across:

http://www.mil.ufl.edu/3701/labs/gcpu/gcpu_files.pdf

Really great project! I loved reading through this diagram. Couple of quick questions, if you don’t mind:

Why are both /AO and /CO active in the second step of your STO instruction?

Have you thought about adding a shift right and shift left operation to your ALU? Really easy to implement… just offset the wires in one direction or the other. Then you can write code to multiply and divide.

Thanks for sharing this, it’s really nice to see someone getting into this stuff.

Are you referring to address 16? That is the second step of the STO op code as you pointed out. During that microinstruction the Accumulator outputs into RAM. In order for my 74189 64-bit RAM to write a byte it needs to have both its write and read pins low. So memory address 16 contains the control word to bring MI_, MO_ and AO_ low.

It is funny that you would mention bit shifting. The other night I was wondering how multiplication was carried out in bitwise operations (I did not know how it officially worked). I concluded that bit shifting was the most efficient option, and it turned out the method that I thought of was already in use. Perhaps if I further this project once it is completed I can add more useful commands such as bit shifting or logical operations.

Thank you, it has been a substantial learning experience for me.

this is great, really inspiring! and your project notes are works of art. great job!

Now there’s something I haven’t seen in a long time! Used to enjoy building 555-timers and logic devices from similar “truth tables”!

I really enjoy reading the blog about this project

I dont want to be rude or anything but a 4 bit address bus is less than useless. You cant do anything with a 4 bit address bus an 8 bit address bus maybe but for anything even semi-useful you need at least a 12 bit address bus. All popular 8 bit computers back in the day used a 16 bit address bus with one using a 14 bit one.

I agree to an extent. The four bit address architecture is the one described in Digital Computer Electronics. I began my design based on the SAP-1 included in that book and therefore it ended up having a 4-bit address line. Having only 16 memory locations is very limiting, but it still is a start. If I were to do the project over again I would most certainly increase the address bit width.

Why not for your second project build a z80 computer? Jameco.com is an excellent parts source and has very cheap drams and srams the z80 even has dram refresh built in if you choose to use dynamic rams. The z80 is an excellent microprocessor and it only costs $2 and drams are 99 cents apeice with srams being $2 – $4s.

I have thought about that a lot. I bought a Z80 processor from them a while back as they were so inexpensive. If I ever were to delve into such a project, I now have the part.

Very nice, orry for all of the questions, I’ve just started designing my own homebrew CPU partly based on your design and I’m trying to work out if there are any obvious things I’ve missed, so “Because I want to” is just as helpful an answer as something more technical

Why does it require 3 microinstructions to do the instruction fetch? If the program counter increment is just a counter then can it not be done at the same time as the opcode being read back from the memory to the IR? Or is it that way because of the time taken for the opcode to appear from the ROM?

You are correct. The increment state could take place during the memory state, but because of each OP taking three T states to operate it is acceptable to separate the processes into three cycles. It is efficient to include a variable machine cycle in which the computer clears the ring counter if a NOP (no operation) condition is present. If you were to combine the increment in memory state this would of course save one T cycle in this case

Is there a particular reason for wanting each op to take three T-states? As the fetch T-states are executed for every instruction, it effectively makes every op take 6 T-states, so reducing the Fetch to 2 T-states would reduce runtime by 16%. I guess you would want to burn off some more clock cycles for a NOP (for example if you are waiting for something to happen) because you would need three times as many NOP instructions in memory to get a 6-clock delay – I’m wondering if there is something else I’ve overlooked.

Sorry for all of the questions, I’ve just started designing my own homebrew CPU partly based on your design and I’m trying to work out if there are any obvious things I’ve missed, so “Because I want to” is just as helpful an answer as something more technical 🙂

It’s fine, ask as many questions as you like. What you are describing is what I was talking about in my previous comment. A variable machine cycle is when the control matrix detects when a NOP control word is present (by using an AND or NAND gate) and clears the ring counter so that the next instruction cycle can begin. I wish you luck with your project.

This is very good amazing!

Websites we think you should visit…

we like to honor many other internet sites on the web, even if they aren’t linked to us, by linking to them. Under are some webpages worth checking out…

You said you used three rom chips, but there were only two in the diagram.

There are two blocks in the diagram, one for the instruction and one for the control word. The control word is 16 bits long and requires two 8-bit ROM chips. (I am assuming that you are talking about this diagram).

How would you add the compare command to your computer.

Why do the ram control bits need to be inverted?